Zurich Instruments

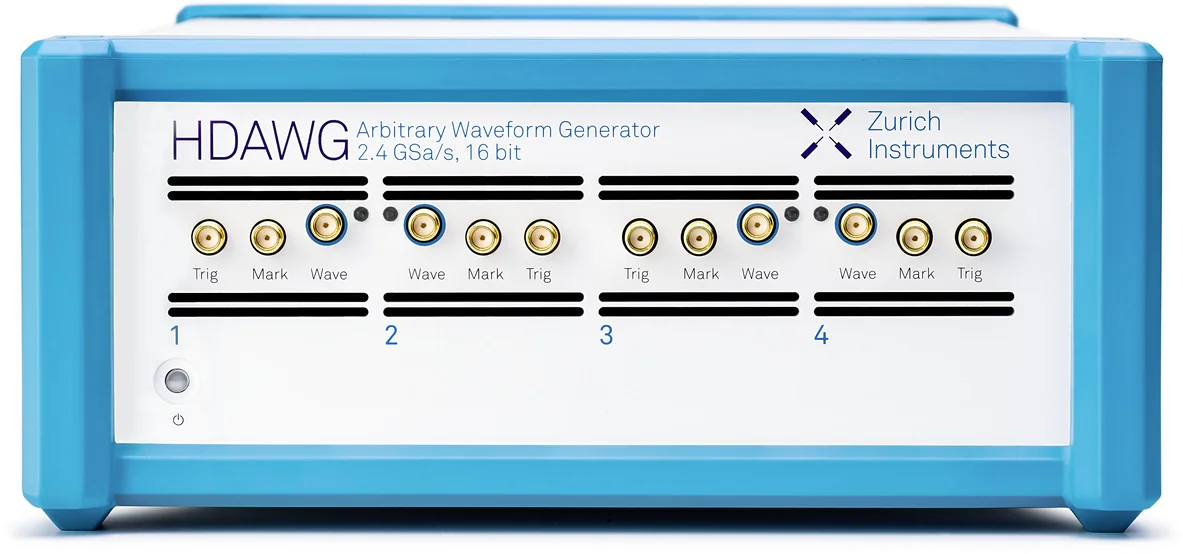

HDAWG 750 MHz Arbitrary Waveform Generator 任意波形產生器

主要特徵

- 2.4 GSa/s、16 位元、750 MHz 訊號頻寬

- 5 Vpp峰值最高值

- 可擴展至 144 個輸出通道

- 高通道密度

- 觸發到輸出延遲小於 50 ns

- 多頻率數位調製

- LabOne ® AWG 排序器和編譯器

- 透過 LabOne ®、LabOne Q 或 API進行控制

規格

Arbitrary waveform generator

| Channels | 4 (HDAWG4 model) 8 (HDAWG8 model) |

| Vertical resolution | 16 bits |

| Waveform memory per channel | 64 MSa; 500 MSa (with HDAWG-ME option) |

| Sequence length | 8,192 |

| Waveform granularity | 16 samples |

| Minimum waveform length | 32 samples |

| Sequencer clock frequency | Sampling rate divided by 8 |

| Sequencer instructions (playback) | Play waveform (single or multi-channel), play waveform from the library (readout results received over ZSync from a PQSC or from the results of the HDAWG-CNT Pulse Counter option) |

| Sequencer instructions (other) | Wait constant, wait for trigger, set/get trigger state, set/get DIO state, integer variable operations (add, subtract, logical operations), change oscillator frequency/phase (real-time), change other instrument setting (non real-time) |

| Sequencer control structures | Repeat (1 to 223-1 or infinite), conditional branch (multi-branch) |

Wave Signal Output

| Connector type | SMA (front panel, single-ended) |

| Output impedance | 50 Ω |

| Output coupling | DC |

| Output modes | Amplified, direct |

| Output range | ±0.1 V to ±2.5 V (amplified, into 50 Ω) ±0.4 V (direct) |

| Output level accuracy | ±(1% of setting + 5 mVpp) (amplified, into 50 Ω) |

| Output level resolution | < 0.1 mV |

| Offset voltage | 0.5 × peak voltage, max. ±1.25 V (amplified, into 50 Ω) 0 V (direct) |

| Offset voltage accuracy | ±(1% of setting + 5 mV) |

| Phase noise | < -135 dBc/Hz (amplified, 1 Vpp, 100 MHz, offset 10 kHz) < -148 dBc/Hz (amplified, 1 Vpp, 100 MHz, offset 1 MHz) < -135 dBc/Hz (direct, 0.5 Vpp, 100 MHz, offset 10 kHz) < -148 dBc/Hz (direct, 0.5 Vpp, 100 MHz, offset 1 MHz) |

| Wave output period jitter | 3 ps RMS (square wave, 150 MHz) |

| Voltage noise above 200 kHz |

35 nV/√Hz (amplified, ±2.5 V range, into high impedance) 12 nV/√Hz (direct, into high impedance) |

| RMS voltage noise (integrated from 100 Hz to 600 MHz) |

320 µVrms (amplified, ±2.5 V range, into 50 Ω) 100 µVrms (direct, into 50 Ω) |

Time- and frequency-domain characteristics

| Wave output bandwidth (-3dB, after correcting for sin(x)/x roll-off) | 0 – 300 MHz (amplified, ±2.5 V range) 0 – 750 MHz (direct) |

| Sampling rate | 100 MSa/s to 2.4 GSa/s |

| Sampling rate divider | 20 to 213 |

| Internal sampling clock resolution | 7 digits |

| Rise time (20% to 80%) | 450 ps (0.2 V step, amplified, ±0.4 V range) 800 ps (1 V step, amplified, ±2.5 V range) 1100 ps (5 V step, amplified, ±2.5 V range) 300 ps (0.8 V step, direct) 550 ps (1 V step, amplified, ±1.5V range) |

| Overshoot | < 1% |

| Trigger delay to output | < 50 ns (within one channel pair 1&2, 2&4, 5&6, 7&8 using playWaveDigTrigger sequencer instruction) < 180 ns (using waitDigTrigger sequencer instruction) |

| Skew between channels | < 200 ps |

| Skew control range | 10 ns |

| Skew control resolution | <0.42 ns (see also this blog post) |

Marker and other outputs

| Marker outputs | 1 per channel, SMA (front panel), 2 marker bits per waveform |

| Marker output impedance | 50 Ω |

| Marker output rise/fall time | 300 ps (20/80%) |

| Marker output period jitter | 60 ps p-p (square wave, 100 MHz) |

| Marker output skew control | -23…30 ns (range, at max. sampling rate) ~10 ps (resolution, at max. sampling rate, depends on absolute setting) |

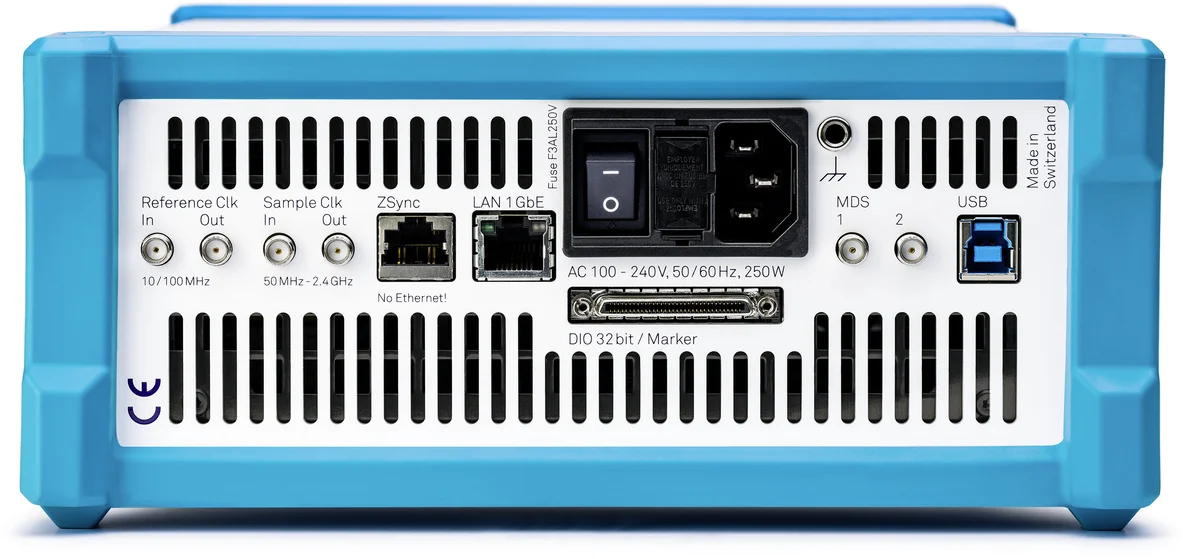

| Sampling clock output | SMA on back panel |

| Sampling clock output amplitude | 0.8 Vpp (2.4 GHz into 50 Ω) 2.0 Vpp (1.0 GHz into 50 Ω) |

| Reference clock output | SMA on back panel |

| Reference clock output impedance | 50 Ω, AC coupled |

| Reference clock output amplitude | 1 Vpp (100 MHz into 50 Ω) |

| Reference clock output frequency | 100 MHz (internal reference mode) 10 / 100 MHz (external reference mode) |

| Reference clock output jitter | 260 fs RMS, derived from integrated phase noise measurement (12 kHz to 200 MHz offset frequency) |

Inputs

| Trigger inputs | 1 per channel, SMA (front panel) |

| Trigger input impedance | 50 Ω / 1 kΩ |

| Trigger input voltage range | ±5 V (50 Ω) ±10 V (1 kΩ) |

| Trigger input threshold range | ±5 V (50 Ω) ±10 V (1 kΩ) |

| Trigger input threshold resolution | < 0.4 mV |

| Trigger input threshold hysteresis | > 60 mV |

| Trigger input min. pulse width | 5 ns |

| Trigger input max. operating frequency | 300 MHz |

| Sampling clock input | SMA (back panel) |

| Reference clock input | SMA (back panel) |

| Reference clock input impedance | 50 Ω, AC coupled |

| Reference clock input frequency | 10 / 100 MHz |

| Reference clock input amplitude | -4 dBm to +13 dBm |

Oscillators and clocks

| Internal clock type | TXCO |

| Internal clock aging | ±0.8 ppm/year |

| Internal clock short-term stability | 0.0001 ppm (1 s) |

| Internal clock initial accuracy | ±1 ppm |

| Internal clock temperature stability | ±0..3 ppm (–20°C to +70°C) |

| Internal clock phase noise | -105 dBc/Hz (offset 100 Hz) -125 dBc/Hz (offset 1 kHz) |

Maximum ratings

| Damage threshold Wave | -1.2 V / +1.2 V (direct) -6 V / +6 V (amplified) |

| Damage threshold Mark | -0.7 / +4 V |

| Damage threshold Trig | -11 V / +11 V (1 kΩ input impedance) -6 V / +6 V (50 Ω input impedance) |

| Damage threshold Reference Clk In | -4 V / +4 V (DC) +13.5 dBm (AC, with DC offset 0 V) |

| Damage threshold Reference Clk Out | -4 V / +4 V (DC) |

| Damage threshold Sample Clk In | -4 V / +4 V (DC) +13.5 dBm (AC, with DC offset 0 V) |

| Damage threshold Sample Clk Out | -4 V / +4 V (DC) |

| Damage threshold MDS In/Out | -0.7 / +4 V |

| Damage threshold DIO In/Out | -0.7 / +4 V (default configuration 3.3 V CMOS/TTL) |

Connectivity and others

| Digital IO (DIO) | VHDCI 68 pin female connector, 32-bit, configurable as input or output, 3.3 V TTL |

| Host connection | LAN/Ethernet, 1 Gbit/s USB 3.0, 5 Gbit/s |

| PC memory requirements | 4 GB+ |

| PC CPU requirements | Compatibility with SSE2 instruction set required. Examples: AMD K8 (Athlon 64, Sempron 64, Turion 64, etc.), AMD Phenom, Intel Pentium 4, Xeon, Celeron, Celeron D, Pentium M, Celeron M, Core, Core 2, Core i5, Core i7, Core i3, Atom |

| PC operating systems | See LabOne Compatibility |

General

| Dimensions | 43.0 × 23.2 × 10.2 cm 16.9 × 9.2 × 4.0 inch, suited for 19 inch rack |

| Weight | 4.6 kg; 10.2 lbs |

| Power supply AC line | 100−240 V (±10%), 50/60 Hz |

| Operating temperature | +5 °C to +40 °C |

| Operating environment | IEC61010, indoor location, installation category II, pollution degree 2 |

| Operating altitude | Up to 2000 m |